# SC8905 High Efficiency, Synchronous, Bi-Directional Buck-Boost Charger Converter with Four Integrated MOSFET

### 1 Descriptions

SC8905 is a synchronous buck-boost charger converter which also supports reverse discharging operation. Four switches are integrated to simplify the system design. SC8905 employs current-mode control and can support very wide input and output voltage range. It can support applications from 2.7V to 22V VBUS range. It is able to effectively manage charging for 2~4 cell batteries no matter input/output voltage is higher, lower or equal to battery voltage. When system needs to discharge from battery, the IC will deliver desired output from the battery.

Through its I2C interface, user can set the charging / discharging mode easily, and program the charging current, VINREG voltage, reversed output voltage adjustment, current limits, switching frequency and other parameters flexibly. Charging voltage and current limit can be adjusted by external resistor.

SC8905 supports internal current limit, under voltage protection, over voltage protection, output short protection and over temperature protections to ensure safety under abnormal conditions.

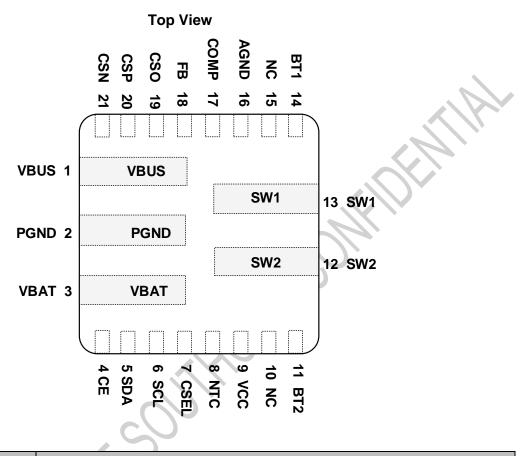

The IC is in a 21 pin 4x4 QFN package.

### 3 Applications

- Power Bank

- USB Power Delivery

- Battery Chargers

### 2 Features

- Buck-Boost Battery Charger for 2 to 4 Cell Batteries

4.2V/4.35V/4.4V for 2s and 3s, 4.2V/4.35V for 4s

- Charging Management: Trickle Charging, CC Charging, CV Charging, Charging Termination, Auto Recharge

- Buck-Boost Reverse Discharging Mode

- Integrated Switches, 10 mΩ for Q1/4, 20 mΩ for Q2/3

- Wide VBAT Range: 2.7 V to 22 V, 25V sustainable

- Wide VBUS Range: 2.7 V to 22 V, 25V sustainable

- High Efficiency Buck-Boost Conversion

- I2C Interface

- Dynamic Output Voltage Control

- Output Voltage Cable Drop Compensation

- Adjustable Switching Frequency

- Programmable Current Limit

- Current Monitor

- NTC Battery temperature protection

- Under Voltage Protection, Over Voltage Protection, Over Current Protection

- Short Protection and Thermal Shutdown Protection

- QFN-21 4 x 4 Package

### 4 Device Information

| Part Number | Package    | Dimension              |

|-------------|------------|------------------------|

| SC8905QFER  | 21 pin QFN | 4.0mm x 4.0mm x 0.75mm |

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

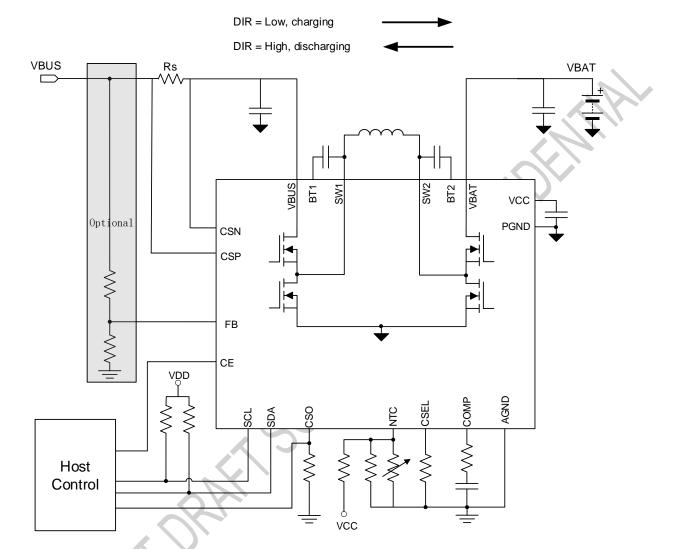

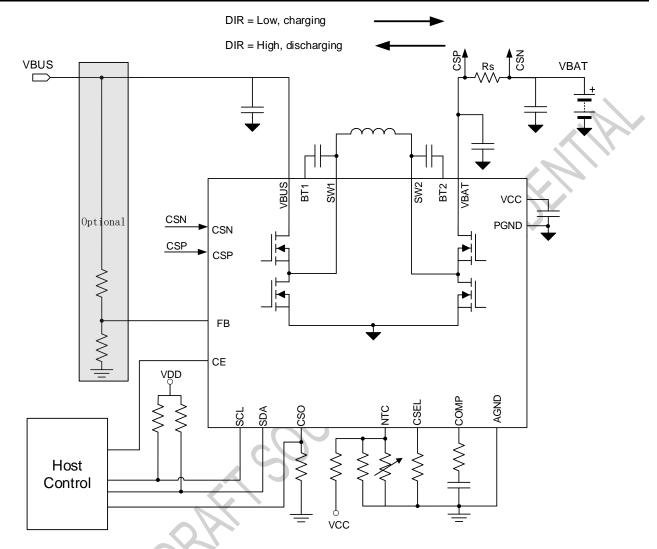

### 5 Typical Application Circuit

Typical application circuit 1. current sense at VBUS

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

Typical application circuit 2. current sense at VBAT

**Note:** User can place current sense resistor at VBUS or VBAT according to application requirement. SC8905 constantly regulates the sense resistor current at setting value, which is decided by internal register and CSO resistor. Please refer to **CC charge/trickle charge/output current limit** for current setting specification.

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

## 6 Terminal Configuration and Functions

| TERMINAL |      | 1/0 | DESCRIPTION                                                                                                                                                                                           |  |

|----------|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NUMBER   | NAME | 1/0 | DESCRIPTION                                                                                                                                                                                           |  |

| 1        | VBUS | I/O | The power input node of the converter in charging mode (DIR = 0), and the power output node of the converter in discharging mode (DIR = 1).                                                           |  |

| 2        | PGND | I/O | Power ground. User shall connect PGND and AGND together on PCB.                                                                                                                                       |  |

| 3        | VBAT | I/O | The power output node of the converter in charging mode (DIR = 0), and the power input node of the converter in discharging mode (DIR = 1). Connect these pins to the positive node of battery cells. |  |

| 4        | CE   | I   | Chip enable pin, active high: pull this pin to logic low to disable the chip. This pin is internally pulled high.                                                                                     |  |

| 5        | SDA  | I/O | I2C interface data. Connect SDA to the logic rail through a pull up resistor (typical 10 k $\Omega$ ).                                                                                                |  |

| 6        | SCL  | I   | I2C interface clock. Connect SCL to the logic rail through a pull up resistor (typical 10 k $\Omega$ ).                                                                                               |  |

| 7        | CSEL | I   | Use this pin to set the battery termination voltage for charging mode. 2s(4.2V,4.35V,4.4V),3s(4.2V,4.35V,4.4V), 4s (4.2V,4.35V).                                                                      |  |

#### SOUTHCHIP SOUTHCHIP SEMICONDUCTOR

SOUTHCHIP CONFIDENTIAL, SUBJECT TO CHANGE

| 8    | NTC  | I   | Connect to the Negative Temperature Coefficient (NTC) thermistor inside the battery cells to sense the battery cells temperature for protection. Short this pin to ground to disable this function. |  |

|------|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 9    | VCC  | 0   | Output of an internal regulator. Connect a 2.2 $\mu$ F ceramic capacitor from VCC to PGND pin close to the IC. The regulator provides supply for internal gate drivers.                             |  |

| 10   | NC   |     | Must be floating.                                                                                                                                                                                   |  |

| 11   | BT2  | I   | Connect a 100nF ceramic capacitor between BT2 pin and SW2 pin to provide the boosted bias voltage for high side gate driver.                                                                        |  |

| 12   | SW2  | I/O | Switching Node 2. Connect to inductor.                                                                                                                                                              |  |

| 13   | SW1  | I/O | Switching Node 1. Connect to inductor.                                                                                                                                                              |  |

| 14   | BT1  | I   | Connect a 100nF ceramic capacitor between BT1 pin and SW1 pin to provide the boosted bias voltage for high side gate driver.                                                                        |  |

| 15   | NC   |     | Must be floating.                                                                                                                                                                                   |  |

| 16   | AGND | I/O | Analog ground. User shall connect PGND and AGND together on PCB.                                                                                                                                    |  |

| 17   | COMP | I   | Connect a RC network to compensate the control loop.                                                                                                                                                |  |

| 18   | FB   | I   | Feedback node of VBUS output voltage. Set the VBUS output voltage in discharging mode by the resistor divider connected at this pin.                                                                |  |

| 19   | CSO  | 0   | Use this pin to monitor the current sensed by CSP and CSN pin. The voltage of CSO is proportional to the sense current.                                                                             |  |

| 20   | CSP  | I   | Positive input of an internal current sense amplifier. Connect a current sense resistor (typical 10 m $\Omega$ ) between CSP and CSN to sense the current.                                          |  |

| 21   | CSN  | 1   | Negative input of an internal current sense amplifier. Connect a current sense resistor (typical 10 m $\Omega$ ) between CSP and CSN to sense the current.                                          |  |

| ORIN |      |     |                                                                                                                                                                                                     |  |